AN-809

ADVANCED SEMICONDUCTOR DEApplication Note P.O. Box 2944, Johannesburg 2000 3rd Floor, Vogas House

123 Pritchard Street/Comer Mool Street a (120) Tel NE 20-2855

## INTERFACING THE MC68000 TO THE MC6846 RIOT

and study on each bas (study up as) could OV and social Prepared by manage and works or base are realized them David Ruhberg Microprocessor Applications Engineer Austin, Texas

The MC6846 ROM I/O Timer (RIOT) provides several versatile functions which the MC68000 may use with minimal effort. The RIOT features a 2K by 8 mask-programmable ROM, an 8-bit I/O port, and a 16-bit programmable timer/ counter, in one forty-pin package. The MC68000 has the option of addressing the RIOT singly or in pairs, depending on the desired bus width. The 8-bit bus can be used if the upper and lower data strobes are used. Note that if a single RIOT is used, the MC68000 will not be able to obtain executable code from the ROM within the RIOT. This is due to the limitation introduced by the width of the data bus on the RIOT. Therefore, to effectively interface the ROM in the RIOT to the MC68000, a 16-bit data bus is used in this application. This configuration makes three 16-bit capabilities available to the MC68000. They are:

- 2K by 16 bits of mask-programmable ROM

- two parallel, 8-bit I/O ports, or one parallel, 16-bit I/O port

- two 16-bit timers that can be used together or independently

## HARDWARE

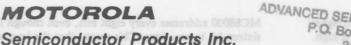

The basic connections needed for the RIOT to function with the MC68000 are: the lower ten address lines (A1-A10), the sixteen data lines (D0-D15), and the R/W, RESET, E, and chip select signals. All of these may be obtained directly from the MC68000 with the exception of the chip select signals. As shown in Figure 1, the eight high-order data lines go to one RIOT and the eight low-order data lines go to the other RIOT. All other connections between the RIOTs are made in parallel. To obtain the chip select signals, some decoding circuitry must be provided. The RIOT may be run synchronously or asynchronously with the MC68000.

Synchronous Operation - To run the RIOT synchronously, some decoding circuitry must be used to provide a low input to the VPA pin of the MC68000 when the RIOT is selected. This synchronizes the MC68000 with E and generates the VMA signal.

To use the synchronous output of the MC68000, the decoding circuitry must also generate a VPA signal, in addition to the chip selects. This signal informs the MC68000 that it is addressing a M6800 peripheral and synchronizes the processor with the E clock. The VPA signal also causes VMA to be generated which can be used for other M6800 peripherals.

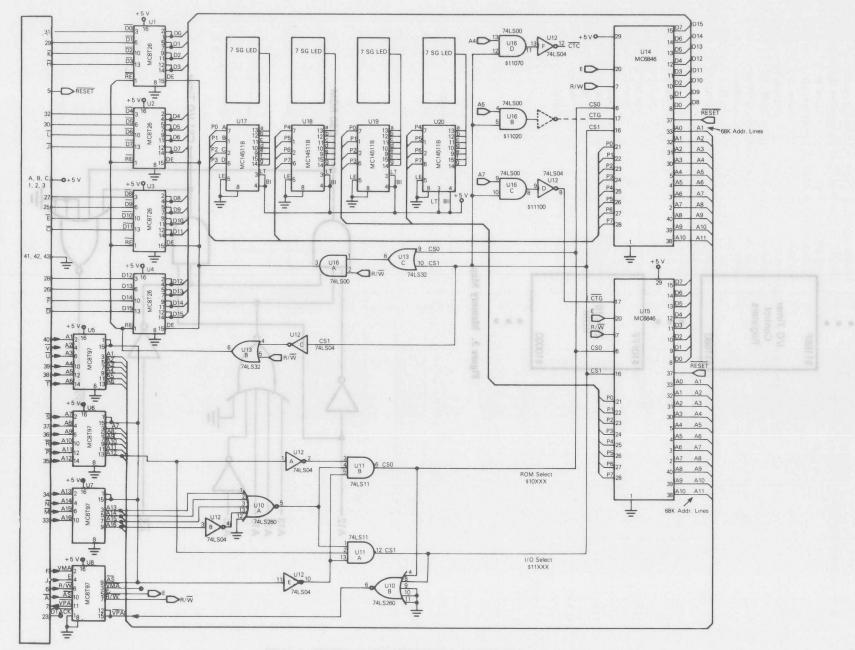

Asynchronous Operation - Operating the RIOTs asynchronously with the MC68000 allows the processor to begin executing the next instruction without waiting to synchronize with the E clock. To operate asynchronously, the decoding circuitry must generate a DTACK signal in addition to the chip selects.

## SAMPLE CIRCUIT

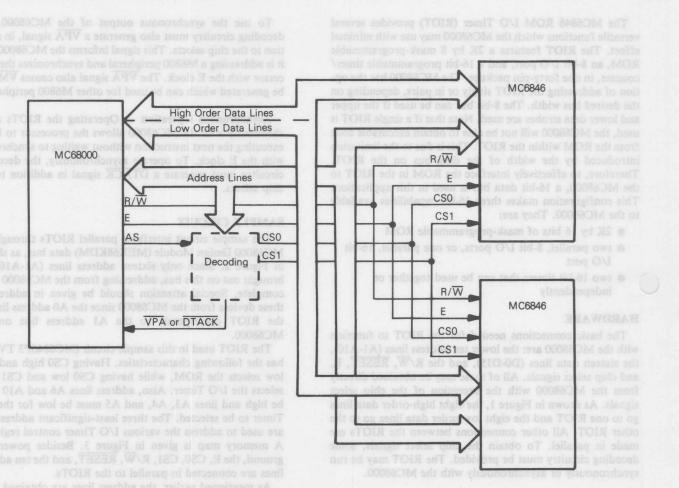

The sample circuit interfaces parallel RIOTs through the MC68000 Design Module (MEX68KDM) data bus, as shown in Figure 2. Since only sixteen address lines (A1-A16) are brought out on this bus, addressing from the MC68000 is incomplete. Special attention should be given in addressing these devices from the MC68000 since the A0 address line on the RIOT corresponds to the A1 address line on the MC68000.

The RIOT used in this sample circuit (MC6846P3 TVBug) has the following characteristics. Having CS0 high and CS1 low selects the ROM, while having CS0 low and CS1 high selects the I/O Timer. Also, address lines A6 and A10 must be high and lines A3, A4, and A5 must be low for the I/O Timer to be selected. The three least-significant address bits are used to address the various I/O Timer control registers. A memory map is given in Figure 3. Besides power and ground, the E, CS0, CS1, R/W, RESET, and the ten address lines are connected in parallel to the RIOTs.

As mentioned earlier, the address lines are obtained from the limited address bus of the Design Module. Buffers are required to reduce noise on the bus lines. Bidirectional, threestateable buffers are used on the data lines so that data may be transmitted to and received from the Module. The receive enable ( $\overline{RE}$ ) signal will go low when R/W is low and the I/O

Timer chip select (CS1) is high. The driver enable (DE) signal will go high when  $R/\overline{W}$  is high and either chip select is high.

The decoding circuitry shown in Figure 4 generates the chip select signals for synchronous operation. A high chip select signal (CS0) is generated for the ROM at addresses \$10000 through \$10FFF. The high chip select signal (CS1) is generated for the I/O Timer registers at addresses \$11880 through \$1188F. The two chip select signals are NORed together to generate the VPA signal. Valid peripheral address should be generated from an open collector gate or passed through a three-stateable buffer to permit a wire-ORed signal.

For asynchronous operation, the U10 NOR gate used to generate VPA is replaced with the TTL circuit shown in Figure 5.

The seven-segment displays are used to show the contents on the parallel I/O data registers in the RIOTs.

Address lines A4, A5, and A7 are decoded to allow software manipulation of the timer contained in each RIOT.

## SOFTWARE

The software needed for the MC68000 to use the RIOT is straightforward. One point to keep in mind is that the MC68000 addresses every eight bits, even though it executes sixteen-bit instructions. This means that the least-significant byte of an instruction is always located at an odd address, and likewise the most-significant byte is always located at an even address. Since the hardware writes to all sixteen bits at once, the addresses for the control registers are located two addresses apart (i.e., PCR: 11882, DDR: 11884, etc.). In using the ROM, no preliminary software is necessary. However, to use the I/O lines, the peripheral control register must be initialized and the data direction register must be configured before data may be transmitted to or received from the peripheral data register.

The software for the sample circuit is given in Figure 6. The I/O lines are connected to four, seven-segment displays through MC14511 BCD-to-decimal decoders. The software initializes the I/O lines (as outputs) and then outputs the first ten bytes of each ROM. Since the decoders cannot decode hexadecimal numbers greater than nine, the software subtracts eight if the number is greater than nine. Then the code is output to the display for operator inspection. This software is included to give you an idea of the simplicity involved in interfacing to these M6800 peripherals.

Synchronous Operation - To run the RIOT Figure 1. MC6846 to MC68000 Interface — Block Diagram

Figure 2. MC6846 to MC68000 Interface - Schematic

w

. . \$1188F I/O Timer Control Registers \$11880 . . . \$10FFF 2K × 16 ROM \$10000 . . . Figure 3. Memory Map A12. CS0 ROM A13 -A14 -A15 -A16 -CS1 I/O Timer AS-VPA

Figure 4. Decoding Circuitry (Synchronous Interface)

Figure 6. Program Listing

| REVII | MC68000 ASM REV= 1.1 - |                      |        | COPYRIGHT BY MOTOROLA 197 |        |            | 1978    |           | PAG             | E 1    |         |

|-------|------------------------|----------------------|--------|---------------------------|--------|------------|---------|-----------|-----------------|--------|---------|

| 1     |                        | 00001000             | OF     | G \$1000                  |        |            |         |           |                 |        |         |

| 2     |                        | 00010000             | ROMSTR | EQU                       | QU     |            | \$10000 |           | *STARTING ADDR. |        |         |

| 3     |                        |                      |        |                           |        |            |         | OF 46 ROM |                 |        |         |

| 4     |                        | 00011882             | PCR    | EQU                       |        | \$11       | 882     |           | *'46 P          |        | •       |

| 5     |                        |                      | * 0    |                           |        |            |         |           | CNTR.           |        |         |

| 6     |                        | 00011884             | DDR    | EQU                       |        | \$11       | 884     |           | *'46 D          |        | IR.     |

| 7     |                        |                      | *      |                           |        |            |         |           | REGIS           |        |         |

| 8     |                        | 00011886             | PDR    | EQU                       |        | \$11       | .886    |           | *'46 P          | ERIPH  |         |

| 9     |                        |                      | *      |                           |        |            |         | DATA      | REG.            |        |         |

| 10    | 001000                 | 33FC0000<br>00011882 |        | MOVE .W                   |        | #\$0       | ,PCR    |           | CONFIG.         | '46    | PCR'S   |

| 11    | 001008                 | 33FCFFFF             |        | SU U2                     |        |            | /       |           |                 |        |         |

|       |                        | 00011884             |        | MOVE .W                   |        | #\$F       | FFF,D   | DR        | CONFIG.         | '46    | DDR'S   |

| 12    | 001010                 | 303C0009             |        | MOVE .W                   |        |            | A-1,D   |           | SET NUM         |        |         |

| 13    |                        |                      | *      | 30                        |        |            |         |           | WORDS F         |        |         |

| 14    |                        |                      | *      |                           |        |            |         |           | TO DISP         |        |         |

| 15    |                        |                      | * *    | *                         | *      | *          | *       | *         | * *             | *      | *       |

| 16    |                        |                      | *      |                           |        |            |         |           |                 |        |         |

| 17    |                        |                      | * 10   | DISPLAY                   | ROUTI  | INE -      | USES    | REGS      | . A1,D0,D1      | .D2.D  | 3       |

| 18    |                        |                      | *      | 10                        |        |            |         |           |                 | ,,     |         |

| 19    |                        |                      | * *    | *                         | *      | *          | *       | *         | * *             | *      | *       |

| 20    |                        |                      | *      |                           |        |            |         |           |                 |        |         |

| 21    |                        |                      | * HEX  | TO DECIN                  | MAL MO | DIFI       | CATIC   | N         | IF HEX DIG      | IT GT  | 9,      |

| 22    |                        |                      | *      |                           |        |            |         |           | SUBTRAC         | T 8    |         |

| 23    | 001014                 | 227C00010000         | CVRCHK | MOVE.L                    |        | #RC        | MSTR,   | Al        | LOAD IN         | STR.   | ADDR.   |

| 24    | 00101A                 | 3211                 | BYTE1  | MOVE .W                   |        | (A1        | .),Dl   |           | FETCH W         | D. FM  | ROM     |

| 25    | 00101C                 | 3401                 |        | MOVE .W                   |        | Dl,        | ,D2     |           | MOVE TO         | SCTC   | H AREA  |

| 26    | 00101E                 | 0242000F             |        | AND.W                     |        | #\$0       | 000F,E  | )2        | ISOLATE         | L.S.   | DIG.    |

| 27    | 001022                 | 0C420009             |        | CMP.W                     |        | #\$0       | 0009,0  | )2        | CHCK IF         | NEED   | S MOD   |

| 28    | 001026                 | 6F000004             |        | BLE                       |        | BYI        | TE2     |           | IF NC           | T, BR  | ANCH    |

| 29    | 00102A                 | 5142                 |        | SUB .W                    |        | #\$0       | 0008,0  | )2        |                 | , SUB  |         |

| 30    | 00102C                 | 3601                 | BYTE2  | MOVE .W                   |        | Dl,        | ,D3     |           | GET S           | ECONE  | BYTE    |

| 31    | 00102E                 | 024300F0             |        | AND.W                     |        | #\$00F0,D3 |         | TO S      | CRATC           | H AREA |         |

| 32    | 001032                 | 0C430090             |        | CMP .W                    |        | #\$0       | 090,0   | )3        | AND             | REPEA  | T PROC  |

| 33    | 001036                 | 6F000006             |        | BLE                       |        | BYI        | re3     |           |                 |        |         |

| 34    | 00103A                 | 04430080             |        | SUB .W                    |        | #\$0       | 080,0   | )3        |                 |        |         |

| 35    | 00103E                 | 8443                 | BYTE3  | OR.W                      |        | D3,        | ,D2     |           |                 |        |         |

|       | 001040                 |                      |        | MOVE .W                   |        |            | ,D3     |           |                 |        |         |

|       |                        | 02430F00             |        | AND .W                    |        |            | DF00,1  |           |                 |        |         |

| 38    | 001046                 | 0C430900             |        | CMP.W                     |        | #\$(       | 0900,1  | )3        |                 |        |         |

| 39    | 00104A                 | 6F000006             |        | BLE                       |        | BYT        | re4     |           |                 |        |         |

| 40    | 00104E                 | 04430800             |        | SUB .W                    |        | #\$(       | 0800,1  | )3        |                 |        |         |

| 41    | 001052                 | 8443                 | BYTE4  | OR.W                      |        | D3,        | ,D2     |           |                 |        |         |

| 42    | 001054                 | 2601                 |        | MOVE .L                   |        |            | ,D3     |           | USE LONG V      | D. FC  | DR MSB. |

| 43    | 001056                 | 02830000F000         |        | AND.L                     |        |            | F000,I  |           |                 |        |         |

| 44    | 00105C                 | 0C8300009000         |        | CMP.L                     |        | #\$9       | 9000,1  | 03        |                 |        |         |

| 45    | 001062                 | 6F000006             |        | BLE                       |        | DON        | NE      |           |                 |        |         |

|       |                        | 04438000             |        | SUB.W                     |        |            | 8000,I  | 03        |                 |        |         |

|       | 00106A                 |                      | DONE   | OR.W                      |        |            | ,D2     |           |                 |        | IN D2   |

|       |                        | 33C200011886         |        | MOVE .W                   |        |            | , PDR   |           | WRITE I         |        |         |

|       |                        | 2E3C0003D090         |        | MOVE .L                   |        |            | 1,0000  | 57        | DLY FOI         | R 5 SE | EC      |

|       | 001078                 |                      | DLY    | SUB.L                     |        |            | ,D7     |           |                 |        |         |

|       | 00107A                 |                      |        | BPL                       |        | DLY        |         |           |                 |        |         |

|       |                        | 51C8FF9C             |        | DBRA                      |        | D0         | ,BYTE   | L         | GO AGN          | IF <>  | > 10    |

| 53    |                        |                      | *      |                           |        |            |         |           |                 |        |         |

Figure 6. Program Listing

NEW YE THDISY900 - I.I =VEN MC

| REVII MC68000 ASM R                    | EV= 1.1 - COPYRIGHT BY MC     | MOROLA 1978     | PAGE 2           |  |  |  |  |  |  |

|----------------------------------------|-------------------------------|-----------------|------------------|--|--|--|--|--|--|

| 54                                     | * BACK TO MACSE               | BUG             |                  |  |  |  |  |  |  |

| 55                                     | *                             |                 |                  |  |  |  |  |  |  |

| 56 001080 4E4F                         | TRAP 15                       |                 |                  |  |  |  |  |  |  |

| 57 001082 0000                         | DC.W (                        | )               |                  |  |  |  |  |  |  |

| 58                                     | *                             |                 |                  |  |  |  |  |  |  |

| 59                                     | * THE PIA ADRESSES ARE        | \$11882 PCR     |                  |  |  |  |  |  |  |

| 60                                     | *                             | \$11884 DDR     |                  |  |  |  |  |  |  |

| 61                                     | *                             | \$11886 TO WRIT | E TO THE DISPL   |  |  |  |  |  |  |

| 62                                     | END                           |                 |                  |  |  |  |  |  |  |

| ***** TOTAL ERRORS 0 0                 |                               |                 |                  |  |  |  |  |  |  |

| SYMBOL TABLE                           |                               |                 |                  |  |  |  |  |  |  |

| BYTE1 00101A BYTE<br>CVRCHK 001014 DDR | 22 00102C BYTE3<br>011884 DLY |                 | 001052<br>00106A |  |  |  |  |  |  |

| PCR 011882 PDR                         | 011886 ROMSTR                 | 010000          |                  |  |  |  |  |  |  |

Figure 6. Program Listing (Concluded)

Metorola reserves the right to make changes to any producin harein to improve reliability. function or design. Metorola doot not assume any inibility artising out of the application of use of any product or sincult described harein, neither doeg it convey any loonize under its patent rights nor the rights of others.

A Semiconductor Products Inc.

|  |  |  | BYTEL<br>CVRCHR<br>• PCR |

|--|--|--|--------------------------|

Figure 6. Program Lizing (Concluded)

Motorola reserves the right to make changes to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

**MOTOROLA** Semiconductor Products Inc. Printed in Switzerland